- 您现在的位置:买卖IC网 > Sheet目录3878 > PIC16F639-E/SO (Microchip Technology)IC MCU FLASH 2KX14 20SOIC

Micrel, Inc.

KSZ8841-PMQL

October 2007

28

M9999-100407-1.5

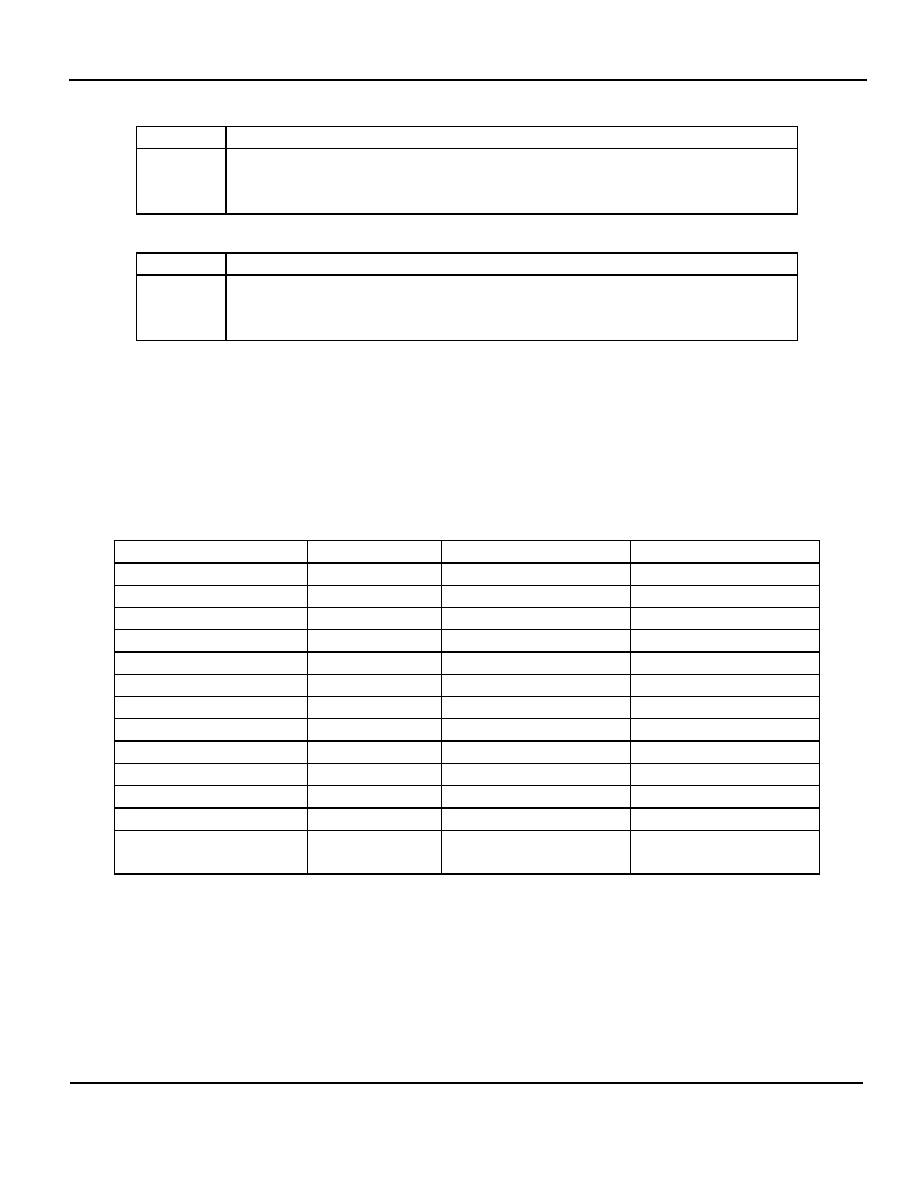

The following table shows the TDES2 register bit fields.

Bit

Description

31 - 0

Buffer Address

Indicates the physical memory address of the buffer.

There is no limitation on the transmit buffer address alignment.

The following table shows the TDES3 register bit fields.

Bit

Description

31 - 0

Next Descriptor Address

Indicates the physical memory address of the next descriptor in the descriptor ring.

The buffer address must be Word aligned.

PCI Configuration Registers

The KSZ8841-PMQL implements 12 configuration registers. These registers are described in the following subsections.

The KSZ8841-PMQL enables a full software-driven initialization and configuration. This allows the software to identify

and query the KSZ8841-PMQL. The KSZ8841-PMQL treats configuration space write operations to registers that are

reserved as no-ops. That is, the access completes normally on the bus and the data is discarded. Read accesses, to

reserved or unimplemented registers, complete normally and a data value of 0 is returned.

Software reset has no effect on the configuration registers. Hardware reset sets the configuration registers to their

default values.

Configuration Register

Identifier

I/O Address Offset

Default

Identification

CFID

0x00

0x884116C6

Command and Status

CFCS

0x04

0x02*00000

Revision

CFRV

0x08

0x02000010

Latency Timer

CFLT

0x0C

0x00000000

Base Memory Address

CBMA

0x10

0x00000000

Reserved

–

0x14-28

0x00000000

Subsystem ID

CSID

0x2C

0x********

Capabilities Pointer

CCAP

0x34

0x********

Reserved

–

0x38

0x00000000

Interrupt

CFIT

0x3C

0x28140100

Reserved

–

0x40-4C

0x00000000

Capability ID

CCID

0x50

0x***20001

Power Management

Control and Status

CPMC

0x54

0x00000000

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24F08KL402-I/SS

IC MCU 16BIT 8KB FLASH 28-SSOP

PIC16F1936-I/MV

IC MCU 8BIT 14KB FLASH 28UQFN

PIC16LF724-I/PT

IC PIC MCU FLASH 7KB 44-TQFP

PIC16F724-I/MV

MCU 7KB FLASH PROGRAM 40-UQFN

PIC16LF724-I/MV

MCU PIC 7KB FLASH XLP 40-UQFN

PIC18F2331T-I/SO

IC MCU FLASH 4KX16 28SOIC

PIC16LF873AT-I/SOG

IC MCU FLASH 4KX14 28SOIC

PIC16LF819T-I/SOG

IC MCU FLASH 2KX14 18SOIC

相关代理商/技术参数

PIC16F639-E/SS

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639-I/P

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639-I/SO

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639-I/SS

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639-I/SS

制造商:Microchip Technology Inc 功能描述:8-Bit Microcontroller IC

PIC16F639T-I/SO

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639T-I/SS

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F648A-E/ML

功能描述:8位微控制器 -MCU 7KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT